# **inter<sub>sil</sub>**

### DATASHEET

### Radiation and SEE Tolerant 3V to 13.2V, 9A Buck Regulator

### ISL70003ASEH

The ISL70003ASEH is an improved version of the ISL70003SEH regulator with both tighter load regulation (<0.3% typical) and a higher output current rating of 9A. Operating over an input voltage range of 3.0V to 13.2V, with integrated low  $r_{DS(ON)}$  MOSFETs makes this monolithic solution highly efficient. Also, a tightly regulated output voltage is possible, which is externally adjustable from 0.6V to ~90% of the input voltage. Continuous output load current capability is 9A for T<sub>J</sub> ≤+125°C and 6A for T<sub>J</sub> ≤+150°C.

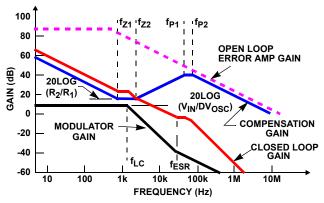

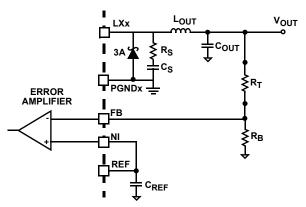

The ISL70003ASEH uses voltage mode control architecture with feed-forward and switches at a selectable frequency of 500kHz or 300kHz. Loop compensation is externally adjustable to allow for an optimum balance between stability and output dynamic performance.

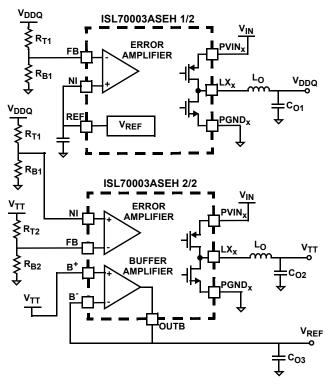

The device features two logic-level disable inputs that can be used to inhibit pulses on the phase (LXx) pins in order to maximize efficiency based on the load current. The ISL70003ASEH also supports DDR applications and contains a buffer amplifier for generating the  $V_{REF}$  voltage.

High integration, best in class radiation performance, and a feature-filled design make the ISL70003ASEH an ideal choice to power many of todays small form-factor applications.

All existing ISL70003SEH supporting collateral is relevant to the ISL70003ASEH and can be used as such.

### Applications

- FPGA, CPLD, DSP, CPU core, and I/O supply voltages

- DDR memory supply voltages

- · Low-voltage, high-density distributed power systems

### **Related Literature**

- · For a full list of related documents, visit our website

- ISL70003ASEH product page

#### 12V INTERMEDIATE BUS ISL70003ASEH ISL75051SEH ISL75051

#### FIGURE 1. POWER DISTRIBUTION SOLUTION FOR RAD HARD LOW POWER FPGA's

### **Features**

- · Acceptance tested to 50krad(Si) (LDR) wafer-by-wafer

- ±1% reference voltage over line, temperature, and radiation

- Integrated MOSFETs 31mΩ PFET/21mΩ NFET

95% peak efficiency

- Externally adjustable loop compensation

- Supports DDR applications (V<sub>TT</sub> tracks V<sub>DD0</sub>/2)

- Buffer amplifier for generating V<sub>REF</sub> voltage

- 3A current sinking capability

- · Grounded lid eliminates charge build up

- IMON pin for output current monitoring

- · Adjustable analog soft-start

- · Diode emulation for increased efficiency at light loads

- 500kHz or 300kHz operating frequency

- · Monotonic start-up into prebiased load

- · Full military temperature range operation

- T<sub>A</sub> = -55°C to +125°C

- T<sub>J</sub> = -55°C to +150°C

- Radiation tolerance

- High dose rate (50-300rad(Si)/s)..... 100krad(Si)

- Low dose rate (0.01rad(Si)/s) ..... 100krad(Si)\*

\* Limit established by characterization.

- SEE hardness

- SEB and SEL LET<sub>TH</sub>  $\dots$  86.4MeV  $\cdot$  cm<sup>2</sup>/mg

- SET at LET 86.4MeV cm<sup>2</sup>/mg .....<±3% ΔV<sub>OUT</sub>

- Electrically screened to DLA SMD <u>5962-14203</u>

### **Table of Contents**

| Functional Block Diagram3                                                                                                                                                                                                                              |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Ordering Information4                                                                                                                                                                                                                                  |

| Pin Configuration5                                                                                                                                                                                                                                     |

| Pin Descriptions5                                                                                                                                                                                                                                      |

| Typical Application Schematics8                                                                                                                                                                                                                        |

| Absolute Maximum Ratings10                                                                                                                                                                                                                             |

| Thermal Information10                                                                                                                                                                                                                                  |

| Recommended Operating Conditions10                                                                                                                                                                                                                     |

| Electrical Specifications10                                                                                                                                                                                                                            |

| Typical Performance Curves13                                                                                                                                                                                                                           |

| Functional Description20                                                                                                                                                                                                                               |

| Power Blocks                                                                                                                                                                                                                                           |

| Initialization                                                                                                                                                                                                                                         |

| Enable         20           Power-On Reset         20           Soft-Start         21           Power-Good         21                                                                                                                                  |

| Fault Monitoring and Protection                                                                                                                                                                                                                        |

| Undervoltage and Overvoltage Monitor.22Undervoltage Protection22Overcurrent Protection22Load Regulation22                                                                                                                                              |

| Application Information23                                                                                                                                                                                                                              |

| Voltage Feed-Forward23Switching Frequency Selection23Synchronization23Output Voltage Selection23Setting the Overcurrent Protection Level23Disabling the Power Blocks23IMON Current Sense Output24Diode Emulation25DDR Application25DDR Configuration26 |

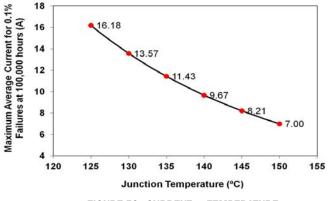

| Operational Envelope 2                                                                                                                                                                                                                                                  | 26                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| High Current Protection Clamp 2                                                                                                                                                                                                                                         | 26                               |

| Derating Current Capability 2                                                                                                                                                                                                                                           | 27                               |

| General Design Guide 2                                                                                                                                                                                                                                                  | 27                               |

| Output Inductor Selection       2         Output Capacitor Selection       2         Input Capacitor Selection       2         Feedback Compensation       2         Modulator Break Frequency Equations       2         Compensation Break Frequency Equations       2 | 27<br>28<br>29<br>29<br>29       |

| PCB Design 3                                                                                                                                                                                                                                                            | 30                               |

| PCB Plane Allocation3PCB Component Placement3LX Connection3Lead Strain Relief3Heatsink Mounting Guidelines3Heatsink Electrical Potential3Heatsink Mounting Materials3                                                                                                   | 30<br>30<br>30<br>30<br>30<br>30 |

| Package Characteristics 3                                                                                                                                                                                                                                               |                                  |

| Weight of Packaged Device         3           Lid Characteristics         3                                                                                                                                                                                             |                                  |

| Die Characteristics 3                                                                                                                                                                                                                                                   | 31                               |

| Die Dimensions    3      Interface Materials    3                                                                                                                                                                                                                       |                                  |

| Metallization Mask Layout 3                                                                                                                                                                                                                                             | 31                               |

| Revision History 3                                                                                                                                                                                                                                                      | 34                               |

| About Intersil                                                                                                                                                                                                                                                          | 34                               |

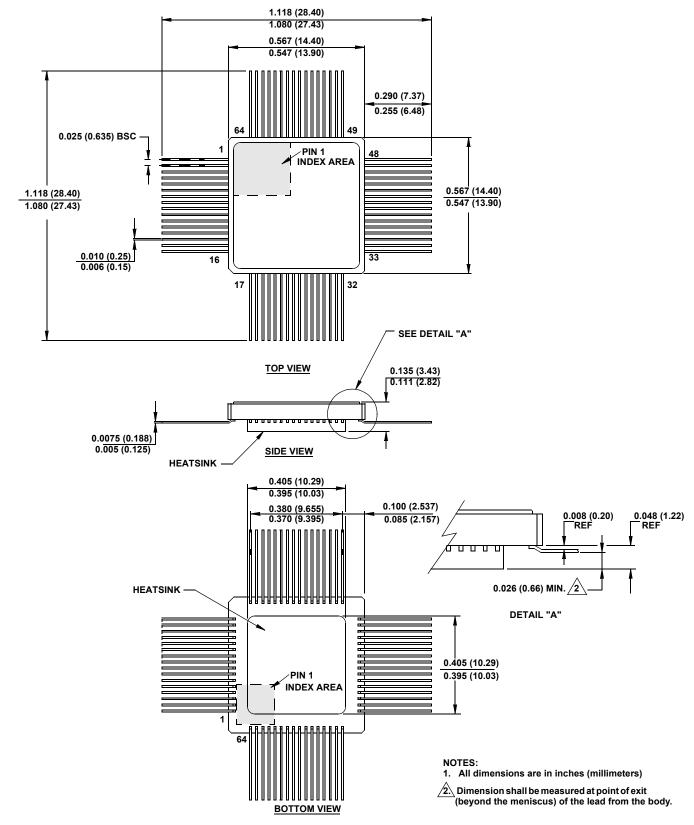

| Package Outline Drawing                                                                                                                                                                                                                                                 | 35                               |

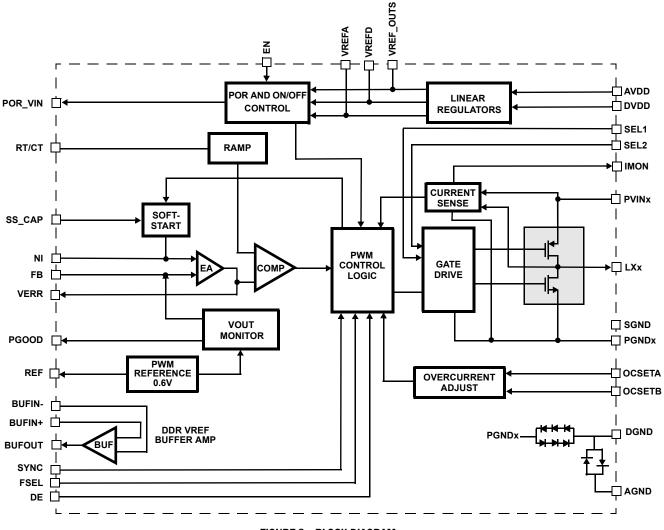

### **Functional Block Diagram**

FIGURE 3. BLOCK DIAGRAM

### **Ordering Information**

| ORDERING SMD<br>NUMBER ( <u>Note 1</u> ) | PART NUMBER<br>( <u>Note 2</u> ) | TEMPERATURE<br>RANGE (°C)          | PACKAGE<br>(Rohs compliant) | PACKAGE<br>DRAWING |  |  |  |

|------------------------------------------|----------------------------------|------------------------------------|-----------------------------|--------------------|--|--|--|

| 5962R1420302VYC                          | ISL70003ASEHVFE                  | -55 to +125                        | 64 Ld CQFP with Heatsink    | R64.C              |  |  |  |

| 5962R1420302V9A                          | ISL70003ASEHVX                   | -55 to +125                        | Die                         |                    |  |  |  |

| N/A                                      | ISL70003ASEHFE/PROTO             | -55 to +125                        | 64 Ld CQFP with Heatsink    | R64.C              |  |  |  |

| N/A                                      | ISL70003ASEHX/SAMPLE             | -55 to +125                        | Die                         |                    |  |  |  |

| N/A                                      | ISL70003ASEHEV1Z                 | Full Featured Evaluation           | Board                       |                    |  |  |  |

| N/A                                      | ISL70003ASEHEV2Z                 | Small Form Factor Evaluation Board |                             |                    |  |  |  |

NOTES:

1. Specifications for Rad Hard QML devices are controlled by the Defense Logistics Agency Land and Maritime (DLA). The SMD numbers listed must be used when ordering.

2. These Intersil Pb-free Hermetic packaged products employ 100% Au plate - e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations.

| PART #       | OUTPUT<br>CURRENT | OUTPUT VOLTAGE LOAD<br>REGULATION |

|--------------|-------------------|-----------------------------------|

| ISL70003SEH  | 6A                | <2%                               |

| ISL70003ASEH | 9A                | <1/2%                             |

#### TABLE 1. DIFFERENCES BETWEEN FAMILY OF PARTS

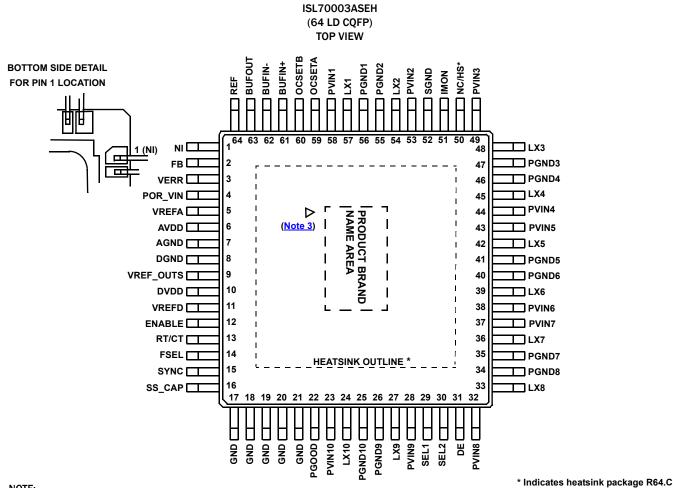

### **Pin Configuration**

NOTE:

3. The ESD triangular mark is indicative of pin #1 location. It is part of the device marking and is placed on the lid in the quadrant where pin #1 is located.

### **Pin Descriptions**

| PIN NUMBER | PIN NAME | ESD CIRCUIT | DESCRIPTION                                                                                                                                                                                                                                                                                     |

|------------|----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | NI       | 1           | This pin is the noninverting input to the internal error amplifier. Connect this pin to the REF pin for typical applications. For DDR memory power applications, connect NI to the BUFOUT pin.                                                                                                  |

| 2          | FB       | 1           | This pin is the inverting input to the internal error amplifier. An external Type III compensation network should be connected between this pin and the VERR pin. The connection between the FB resistor divider and the output inductor should be a Kelvin connection to optimize performance. |

| 3          | VERR     | 1           | This pin is the output of the internal error amplifier. An external compensation network should be connected between this pin and the FB pin.                                                                                                                                                   |

| 4          | POR_VIN  | 1           | This pin is the power-on reset input to the IC. This is a comparator-type input with a rising threshold of 0.6V and programmable hysteresis. Driving this pin above 0.6V enables the IC. Bypass this pin to AGND with a 10nF ceramic capacitor to mitigate SEE.                                 |

| 5          | VREFA    | 3           | This pin is the output of the internal linear regulator and the bias supply input to the internal analog control circuitry. Locally filter this pin to AGND using a $0.47\mu$ F ceramic capacitor as close as possible to the IC.                                                               |

| 6          | AVDD     | 5           | This pin provides the supply for the internal linear regulator of the ISL70003ASEH. The supply to AVDD should be locally bypassed using a ceramic capacitor. Tie AVDD to the PVINx pins.                                                                                                        |

### Pin Descriptions (Continued)

| PIN NUMBER                                   | PIN NAME  | ESD CIRCUIT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------|-----------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7                                            | AGND      | 1, 3        | This pin is the analog ground associated with the internal analog control circuitry. Connect this pin directly to the PCB ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8                                            | DGND      | 2, 4        | This pin is the ground associated with the internal digital control circuitry. Connect this pin directly to the PCB ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9                                            | VREF_OUTS | 4           | This pin is the output of the internal linear regulator and the supply input to the internal reference circuit. Locally filter this pin to AGND using a 0.47µF ceramic capacitor as close as possible to the IC.                                                                                                                                                                                                                                                                                                                                                        |

| 10                                           | DVDD      | 6           | This pin provides the supply for the internal linear regulator of the ISL70003ASEH. The supply to DVDD should be locally bypassed using a ceramic capacitor. Tie DVDD to the PVINx pin.                                                                                                                                                                                                                                                                                                                                                                                 |

| 11                                           | VREFD     | 4           | This pin is the output of the internal linear regulator and the bias supply input to the internal digital control circuitry. Locally filter this pin to DGND using a 0.47µF ceramic capacitor as close as possible to the IC.                                                                                                                                                                                                                                                                                                                                           |

| 12                                           | ENABLE    | 6           | This pin is a logic-level enable input. Pulling this pin low powers down the device by placing it into a very low-power Sleep mode.                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13                                           | RT/CT     | 6           | A resistor to VIN and a capacitor to GND provide feed-forward to keep a constant modulator gain of 4.8 as VIN varies.                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 14                                           | FSEL      | 2           | This pin is the oscillator frequency select input. Tie this pin to 5V to select a 300kHz nominal oscillator frequency. Tie this pin to the PCB ground plane to select a 500kHz nominal oscillator frequency.                                                                                                                                                                                                                                                                                                                                                            |

| 15                                           | SYNC      | 2           | This pin is the frequency synchronization input to the IC. This pin should be tied to GND to free-run from the internal oscillator or connected to an external clock for external frequency synchronization.                                                                                                                                                                                                                                                                                                                                                            |

| 16                                           | SS_CAP    | 2           | This pin is the soft-start input. Connect a ceramic capacitor from this pin to the PCB ground plane to set<br>the soft-start output ramp time in accordance with Equation 1:<br>$t_{SS} = C_{SS} \cdot V_{REF} / I_{SS}$ (EQ. 1)                                                                                                                                                                                                                                                                                                                                        |

|                                              |           |             | where:<br>$t_{SS}$ = soft-start output ramp time<br>$C_{SS}$ = soft-start capacitance<br>$V_{REF}$ = reference voltage (0.6V typical)<br>$I_{SS}$ = soft-start charging current (23µA typical)<br>Soft-start time is adjustable from approximately 2ms to 200ms. The range of the soft-start capacitor<br>should be 82nF to 8.2µF, inclusive.                                                                                                                                                                                                                           |

| 17, 18, 19, 20, 21                           | GND       | 2           | Connect these pin to the PCB ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 22                                           | PGOOD     | 6           | This pin is the power-good output. This pin is an open-drain logic output that is pulled to DGND when<br>the output voltage is outside a $\pm 11\%$ typical regulation window. This pin can be pulled up to any voltage<br>from OV to 13.2V, independent of the supply voltage. A nominal $1\kappa\Omega$ to $10\kappa\Omega$ pull-up resistor is<br>recommended. Bypass this pin to the PCB ground plane with a 10nF ceramic capacitor to mitigate SEE.                                                                                                                |

| 23, 28, 32, 37,<br>38, 43, 44, 49,<br>53, 58 | PVINx     | 7           | These pins are the power supply inputs to the corresponding internal power blocks. These pins must be connected to a common power supply rail, which should fall in the range of 3V to 13.2V. Bypass these pins directly to PGNDx with ceramic capacitors located as close as possible to the IC. When sinking current or at a no load condition, the inductor valley current will be negative. During any time when the inductor valley current is negative and the ISL70003ASEH is exposed to a heavy ion environment, the abs max PVIN voltage must be $\leq$ 13.7V. |

| 29                                           | SEL1      | 2           | This pin is a logic-level disable (high) input working in conjunction with SEL2. These pins form a 2-bit logic input that set the number of active power blocks. This allows the ISL70003ASEH current capability to be tailored to the load current level the application requires and achieve the highest possible efficiency.                                                                                                                                                                                                                                         |

| 30                                           | SEL2      | 2           | This pin is a logic-level disable input. Pulling this pin high inhibits pulses on the LXx outputs. See description of Pin 29, SEL1, for more information.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 31                                           | DE        | 2           | The DE pin enables or disables diode emulation. When it is HIGH, diode emulation is allowed.<br>Otherwise, Continuous Conduction mode is forced.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 24, 27, 33, 36,<br>39, 42, 45, 48,<br>54, 57 | LXx       |             | These pins are the switch node connections to the internal power blocks and should be connected to the output filter inductor. Internally, these pins are connected to the synchronous MOSFET power switches.                                                                                                                                                                                                                                                                                                                                                           |

### Pin Descriptions (Continued)

| PIN NUMBER                                   | PIN NAME | ESD CIRCUIT               | DESCRIPTION                                                                                                                                                                                                                                                                                  |  |  |  |  |

|----------------------------------------------|----------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 50                                           | HS       | N/A                       | On the R64.C package (heatsink option) this pin is electrically connected to the heatsink on the underside of the package. Connect this pin and/or the heatsink to a thermal plane.                                                                                                          |  |  |  |  |

| 51                                           | IMON     | 1                         | IMON is a current source output that is proportional to the sensed current through the regulator. If no<br>used it is recommended to tie IMON to VREFA. It is also acceptable to tie IMON to GND through a<br>resistor.                                                                      |  |  |  |  |

| 52                                           | SGND     | 1                         | This pin is connected to an internal metal trace that serves as a noise shield. Connect this pin to the PCB ground plane.                                                                                                                                                                    |  |  |  |  |

| 25, 26, 34, 35,<br>40, 41, 46, 47,<br>55, 56 | PGNDx    | 7                         | These pins are the power grounds associated with the corresponding internal power blocks. Connect hese pins directly to the PCB ground plane. These pins should also connect to the negative terminals of the input and output capacitors. The package lid is internally connected to PGNDx. |  |  |  |  |

| 59                                           | OCSETA   | 3                         | This pin is the redundant output overcurrent set input. Connect a resistor from this pin to the PCB ground plane to set the output overcurrent threshold.                                                                                                                                    |  |  |  |  |

| 60                                           | OCSETB   | 3                         | This pin is the primary output overcurrent set input. Connect a resistor from this pin to the PCB ground plane to set the output overcurrent threshold.                                                                                                                                      |  |  |  |  |

| 61                                           | BUFIN+   | 1                         | his pin is the input to the internal unity gain buffer amplifier. For DDR memory power applications, ponnect the VTT voltage to this pin.                                                                                                                                                    |  |  |  |  |

| 62                                           | BUFIN-   | 1                         | This pin is the inverting input to the buffer amplifier. For DDR memory power applications, connect BUFOUT to this pin. Bypass this pin to the PCB ground plane with a 0.1µF ceramic capacitor.                                                                                              |  |  |  |  |

| 63                                           | BUFOUT   | 3                         | This pin is the output of the buffer amplifier. In DDR power applications, connect this pin to the reference input of the DDR memory. The buffer needs a minimum of 1.0μF load capacitor for stability                                                                                       |  |  |  |  |

| 64                                           | REF      | 1                         | This pin is the output of the internal reference voltage. Bypass this pin to the PCB ground plane with a 220nF ceramic capacitor located as close as possible to the IC. The bypass capacitor is needed to mitigate SEE.                                                                     |  |  |  |  |

| VREFA                                        |          |                           | #     7v     7v     18v       clamp     GNDA     GNDA     GNDA                                                                                                                                                                                                                               |  |  |  |  |

| 18V<br>CLAMP<br>CIRCUIT 6                    |          | 18V<br>CLAMP<br>CIRCUIT 7 |                                                                                                                                                                                                                                                                                              |  |  |  |  |

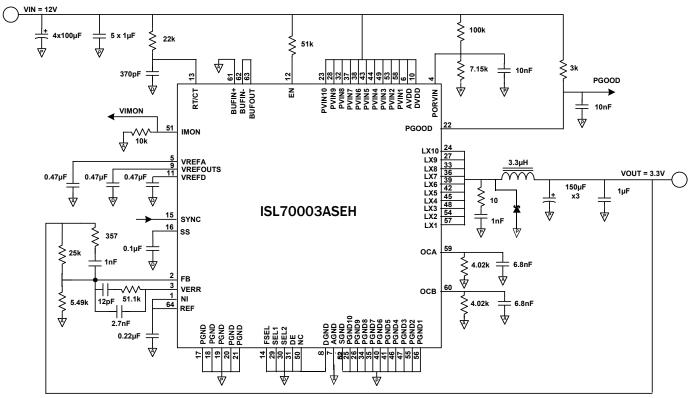

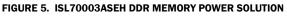

### **Typical Application Schematics**

FIGURE 4. ISL70003ASEH SINGLE UNIT OPERATION

#### Typical Application Schematics (Continued)

#### **Absolute Maximum Ratings**

| LXx, PVINx (PGNDx - 0.3V) to PGNDx + 16V                                 |

|--------------------------------------------------------------------------|

| LXx, PVINx ( <u>Note 4</u> )(PGNDx - 0.3V) to PGNDx + 14.7V              |

| LXx, PVINx ( <u>Note 5</u> )(PGNDx - 0.3V) to PGNDx + 13.7V              |

| AVDD - AGND, DVDD - DGND PVINx to -0.3V                                  |

| VREFA(GNDA - 0.3V) to GNDA + 5.5V                                        |

| VREFD, VREF_OUTS (GNDD - 0.3V) to GNDD + 5.5V                            |

| Signal Pins ( <u>Note 8</u> ) (GNDA - 0.3V) to VREFA + 0.3V              |

| Digital Control Pins ( <u>Note 9</u> ) (GNDD - 0.3V) to VREFD+ 0.3V      |

| SS_CAP (DGND - 0.3V) to DGND + 2.5V                                      |

| PGOOD                                                                    |

| RT/CT(GNDD - 0.3V) to DVDD                                               |

| Sourcing Output DC Current T <sub>J</sub> ≤+125°C (All Power Blocks) 11A |

| Sourcing Output DC Current T <sub>J</sub> ≤+150°C (All Power Blocks) 7A  |

| Sinking Output DC Current T <sub>J</sub> ≤+125°C (All Power Blocks)4A    |

| ESD Rating                                                               |

| Human Body Model (Tested per MIL-STD-883 TM3015.7) 2kV                   |

| Machine Model (Tested per JESD22-A115-A)                                 |

| Charge Device Model (Tested per JESD22-C101D) 750V                       |

#### **Thermal Information**

| Thermal Resistance (Typical)                     | θ <sub>JA</sub> (°C/W) | θ <sub>JC</sub> (°C/W) |

|--------------------------------------------------|------------------------|------------------------|

| CQFP Package R64.C ( <u>Notes 6</u> , <u>7</u> ) | 17                     | 0.7                    |

| Maximum Junction Temperature                     |                        | +150°C                 |

| Storage Temperature Range                        | 6                      | 5°C to +150°C          |

#### **Recommended Operating Conditions**

| Temperature                                            |                       |

|--------------------------------------------------------|-----------------------|

| PVINx, AVDD, DVDD                                      | 3.3V ±10% to 12V ±10% |

| Output DC Current T <sub>J</sub> ≤+125°C (All Power E  | llocks) ≤9A           |

| Output DC Current T <sub>J</sub> ≤+150 °C (All Power E | llocks) ≤6A           |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

NOTES:

- 4. For operation in a heavy ion environment at LET = 86.4 MeV  $\cdot$  cm<sup>2</sup>/mg at +125 °C (T<sub>C</sub>) and sourcing 11A load current.

- 5. For operation in a heavy ion environment at LET = 86.4MeV cm<sup>2</sup>/mg at +125 °C (T<sub>C</sub>) with any negative inductor current to sinking -4A load current.

- 6. θ<sub>JA</sub> is measured in free air with the component mounted on a high-effective thermal conductivity test board with "direct attach" features. See Tech Brief <u>TB379</u>.

- 7. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal heatsink on the package underside.

- 8. POR\_VIN, FB, NI, VERR, OCSETA, OCSETB, BUFOUT, BUFIN-, BUFIN+, IMON, and REF pins.

- 9. FSEL, EN, SYNC, SEL1, SEL2, and DE pins.

**Electrical Specifications** Unless otherwise noted, PVINx = AVDD = DVDD = 3V - 13.2V; GND = AGND = DGND = PGNDx = SGND = 0V; POR\_V<sub>IN</sub> = 0.65V; SYNC = LXx = Open Circuit; PGOOD is pulled up to VREFD with a 3k resistor; REF is bypassed to GND with a 220nF capacitor; SS is bypassed to GND with a 100nF capacitor; I<sub>OUT</sub> = 0A; T<sub>A</sub> = T<sub>J</sub> = +25°C. (<u>Note 4</u>). Boldface limits apply across the operating temperature range, -55°C to +125°C; over a total ionizing dose of 100krad(Si) with exposure at a high dose rate of 50 to 300rad(Si)/s; or over a total ionizing dose of 50krad(Si) with exposure at a low dose rate of <10mrad(Si)/s.

| PARAMETER                | TEST CONDITIONS                                       | MIN<br>( <u>Note 13</u> ) | TYP | MAX<br>( <u>Note 13</u> ) | UNIT |

|--------------------------|-------------------------------------------------------|---------------------------|-----|---------------------------|------|

| POWER SUPPLY             |                                                       |                           |     |                           |      |

| Operating Supply Current | PV <sub>INx</sub> = 13.2V, FSEL = 1 (300kHz)          |                           | 80  | 125                       | mA   |

|                          | PV <sub>INx</sub> = 13.2V, FSEL = 0 (500kHz)          |                           | 80  | 125                       | mA   |

|                          | PV <sub>INx</sub> = 3.0V, FSEL = 1 (300kHz)           |                           | 30  | 60                        | mA   |

|                          | PV <sub>INx</sub> = 3.0V, FSEL = 0 (500kHz)           |                           | 30  | 60                        | mA   |

| Standby Supply Current   | PV <sub>INx</sub> = 13.2V, SEL1 = SEL2 = 5V, FSEL = 1 |                           | 20  | 30                        | mA   |

|                          | PV <sub>INX</sub> = 13.2V, SEL1 = SEL2 = 5V, FSEL = 0 |                           | 20  | 30                        | mA   |

|                          | PV <sub>INX</sub> = 3.0V, SEL1 = SEL2 = 5V, FSEL = 1  |                           | 10  | 15                        | mA   |

|                          | PV <sub>INx</sub> = 3.0V, SEL1 = SEL2 = 5V, FSEL = 0  |                           | 10  | 15                        | mA   |

| Shutdown Supply Current  | $PV_{INX} = 13.2V, EN = GND$                          |                           | 1.5 | 3.0                       | mA   |

|                          | PV <sub>INX</sub> = 3.0V, EN = GND                    |                           | 0.4 | 1.0                       | mA   |

| LINEAR REGULATORS        |                                                       |                           |     |                           |      |

| Output Voltage           | AVDD, DVDD = 13.2V                                    | 4.5                       | 5.0 | 5.5                       | v    |

| Current Limit            | AVDD, DVDD = 13.2V                                    | 50                        |     | 190                       | mA   |

**Electrical Specifications** Unless otherwise noted, PVINx = AVDD = DVDD = 3V - 13.2V; GND = AGND = DGND = PGNDx = SGND = 0V; POR\_V<sub>IN</sub> = 0.65V; SYNC = LXx = Open Circuit; PGOOD is pulled up to VREFD with a 3k resistor; REF is bypassed to GND with a 220nF capacitor; SS is bypassed to GND with a 100nF capacitor; I<sub>OUT</sub> = 0A; T<sub>A</sub> = T<sub>J</sub> =  $+25^{\circ}$ C. (Note 4). Boldface limits apply across the operating temperature range,  $-55^{\circ}$ C to  $+125^{\circ}$ C; over a total ionizing dose of 100krad(Si) with exposure at a high dose rate of 50 to 300rad(Si)/s; or over a total ionizing dose of 50krad(Si) with exposure at a low dose rate of <10mrad(Si)/s. (Continued)

| PARAMETER                                             | TEST CONDITIONS                                            | MIN<br>( <u>Note 13</u> ) | ТҮР   | MAX<br>( <u>Note 13</u> ) | UNIT         |

|-------------------------------------------------------|------------------------------------------------------------|---------------------------|-------|---------------------------|--------------|

| POWER-ON RESET                                        |                                                            |                           |       | -                         |              |

| POR Pin Input Voltage                                 |                                                            | 0.56                      | 0.60  | 0.64                      | v            |

| POR Sink Current                                      |                                                            | 9.6                       | 12    | 14.4                      | μΑ           |

| ENABLE                                                |                                                            |                           |       | L                         |              |

| Enable V <sub>IH</sub> Voltage                        |                                                            | 2                         |       |                           | v            |

| Enable V <sub>IL</sub> Voltage                        |                                                            |                           |       | 0.8                       | v            |

| Enable (EN) Leakage                                   | EN = 4.5V                                                  |                           | 1.0   | 10                        | μΑ           |

| SELECT PHASE                                          |                                                            |                           |       | L                         |              |

| SEL 1, 2 V <sub>IH</sub> Voltage                      |                                                            | 2                         |       |                           | v            |

| SEL 1, 2 V <sub>IL</sub> Voltage                      |                                                            |                           |       | 0.8                       | v            |

| SEL 1, 2 Leakage Current                              | SEL1, 2 = VREFD                                            |                           | 1.0   | 10                        | μΑ           |

| PWM CONTROL LOGIC                                     |                                                            |                           |       | L                         |              |

| Switching Frequency                                   | FSEL = 1                                                   | 255                       | 300   | 345                       | kHz          |

|                                                       | FSEL = 0                                                   | 425                       | 500   | 575                       | kHz          |

| Minimum On-Time                                       | SS = GND ( <u>Note 12</u> )                                |                           | 250   | 320                       | ns           |

| Minimum On-Time                                       | ( <u>Note 12</u> )                                         |                           | 160   | 220                       | ns           |

| Minimum Off-Time                                      | ( <u>Note 12</u> )                                         |                           | 200   | 270                       | ns           |

| Modulator Gain (V <sub>IN</sub> /ΔV <sub>OSC</sub> )  | $R_{T} = 22k\Omega, C_{T} = 370pF, FSEL = 0$               |                           | 5     |                           | V/V          |

|                                                       | $R_{T} = 36k\Omega, C_{T} = 370pF, FSEL = 1$               |                           | 4.8   |                           | V/V          |

| External Synchronization Frequency Range              | FSEL = 1, PV <sub>INx</sub> = 3.0V                         | 255                       | 300   | 345                       | kHz          |

|                                                       | FSEL = 0, PV <sub>INx</sub> = 3.0V                         | 425                       | 500   | 575                       | kHz          |

| SYNC V <sub>IH</sub> Voltage                          |                                                            | 2                         |       |                           | v            |

| SYNC V <sub>IL</sub> Voltage                          |                                                            |                           |       | 0.8                       | v            |

| Synchronization Input Leakage Current                 | SYNC = VREFD                                               |                           | 1.0   | 4                         | μΑ           |

| SOFT-START                                            |                                                            | I                         |       |                           |              |

| Soft-Start Source Current                             | SS = GND                                                   | 20                        | 23    | 27                        | μΑ           |

| Soft-Start Discharge ON-Resistance                    |                                                            |                           | 3.0   | 6.0                       | Ω            |

| Soft-Start Discharge Time                             | ( <u>Note 12</u> )                                         |                           | 256   |                           | Clock Cycles |

| REFERENCE VOLTAGE                                     |                                                            | I                         |       | 1                         |              |

| Reference Voltage Tolerance                           | V <sub>REF</sub> including Error Amplifier V <sub>IO</sub> | 0.594                     | 0.600 | 0.606                     | v            |

| LOAD REGULATION                                       | 1                                                          | 1                         |       | 1                         |              |

| Output Voltage Tolerance Over Output<br>Current Range | PVIN = 3V - 13.2V, to 9A<br>(Notes 11, 12)                 | -0.45                     | -0.05 | 0.25                      | %            |

**Electrical Specifications** Unless otherwise noted, PVINx = AVDD = DVDD = 3V - 13.2V; GND = AGND = DGND = PGNDx = SGND = 0V; POR\_V<sub>IN</sub> = 0.65V; SYNC = LXx = Open Circuit; PGOOD is pulled up to VREFD with a 3k resistor; REF is bypassed to GND with a 220nF capacitor; SS is bypassed to GND with a 100nF capacitor; I<sub>OUT</sub> = 0A; T<sub>A</sub> = T<sub>J</sub> =  $+25^{\circ}$ C. (Note 4). Boldface limits apply across the operating temperature range,  $-55^{\circ}$ C to  $+125^{\circ}$ C; over a total ionizing dose of 100krad(Si) with exposure at a high dose rate of 50 to 300rad(Si)/s; or over a total ionizing dose of 50krad(Si) with exposure at a low dose rate of <10mrad(Si)/s. (Continued)

| PARAMETER                                     | TEST CONDITIONS                                                              | MIN<br>( <u>Note 13</u> ) | ТҮР  | MAX<br>( <u>Note 13</u> ) | UNIT |

|-----------------------------------------------|------------------------------------------------------------------------------|---------------------------|------|---------------------------|------|

| ERROR AMPLIFIER                               |                                                                              |                           |      |                           |      |

| DC Gain                                       | ( <u>Note 12</u> )                                                           |                           | 80   |                           | dB   |

| Gain-Bandwidth Product                        | ( <u>Note 12</u> )                                                           |                           | 7    |                           | MHz  |

| Maximum Output Voltage                        | V <sub>IN</sub> = 5.5V                                                       | 3.5                       | 4.2  |                           | v    |

| Slew Rate                                     | (Note 12)                                                                    |                           | 8.5  |                           | V/µs |

| Feedback (FB) Input Leakage Current           | V <sub>FB</sub> = 0.6V, PV <sub>INx</sub> = 13.2V                            |                           |      | 250                       | nA   |

| Offset Voltage (V <sub>IO</sub> )             |                                                                              | -3                        | 0    | 3                         | mV   |

| POWER BLOCKS                                  |                                                                              |                           |      | 11                        |      |

| CQFP Individual Upper FET r <sub>DS(ON)</sub> | PV <sub>INx</sub> = 3.0V, PVIN to LX                                         | 170                       | 420  | 700                       | mΩ   |

|                                               | PV <sub>INx</sub> = 5.5V, PVIN to LX                                         | 120                       | 310  | 600                       | mΩ   |

| CQFP Individual Lower FET r <sub>DS(ON)</sub> | PV <sub>INx</sub> = 3.0V, LX to GND                                          | 90                        | 240  | 455                       | mΩ   |

|                                               | PV <sub>INx</sub> = 5.5V, LX to GND                                          | 60                        | 210  | 425                       | mΩ   |

| LXx Output Leakage                            | EN = LXx = GND, single LXx output                                            |                           | 1    | 3                         | μA   |

|                                               | $EN = GND$ , $LXx = PV_{INx}$ , Single LXx Output                            |                           | 1    | 3                         | μA   |

| Dead Time                                     | Within a single power block or between power blocks ( <u>Note 12</u> )       | 4                         |      |                           | ns   |

| POWER-GOOD SIGNAL                             |                                                                              | <u> </u>                  |      | 1                         |      |

| Rising Threshold                              | V <sub>FB</sub> as a % of V <sub>REF</sub>                                   | <b>107</b> 111            |      | 115                       | %    |

| Rising Hysteresis                             | V <sub>FB</sub> as a % of V <sub>REF</sub>                                   | 2                         | 3.5  | 5                         | %    |

| Falling Threshold                             | V <sub>FB</sub> as a % of V <sub>REF</sub>                                   | 85                        | 89   | 93                        | %    |

| Falling Hysteresis                            | V <sub>FB</sub> as a % of V <sub>REF</sub>                                   | 2                         | 3.5  | 5                         | %    |

| Power-Good Drive                              | $PV_{IN} = 3V$ , PGOOD = 0.4V, EN = GND                                      | 7.2                       |      |                           | mA   |

| Power-Good Leakage                            | PV <sub>IN</sub> = PG00D = 13.2V                                             |                           |      | 1                         | μA   |

| PROTECTION FEATURES                           |                                                                              |                           |      | 11                        |      |

| Undervoltage Protection                       |                                                                              |                           |      |                           |      |

| Undervoltage Trip Threshold                   | $V_{\mbox{\scriptsize FB}}$ as a % of $V_{\mbox{\scriptsize REF}}$ test mode | 71                        | 75   | 79                        | %    |

| Undervoltage Recovery Threshold               | $V_{\mbox{\scriptsize FB}}$ as a % of $V_{\mbox{\scriptsize REF}}$ test mode | 86                        | 90   | 94                        | %    |

| Overcurrent Protection                        |                                                                              |                           |      | · · · · · ·               |      |

| Overcurrent Accuracy                          | ROCSETA, B = $6k\Omega$ (IOC = $0.6A/LX$ ) V <sub>IN</sub> = $12V$           | 0.43                      | 0.60 | 0.77                      | A/LX |

**Electrical Specifications** Unless otherwise noted, PVINx = AVDD = DVDD = 3V - 13.2V; GND = AGND = DGND = PGNDx = SGND = 0V;  $POR_V_{IN} = 0.65V$ ; SYNC = LXx = Open Circuit; PGOOD is pulled up to VREFD with a 3k resistor; REF is bypassed to GND with a 220nF capacitor; SS is bypassed to GND with a 100nF capacitor;  $I_{OUT} = 0A$ ;  $T_A = T_J = +25$ °C. (Note 4). Boldface limits apply across the operating temperature range, -55°C to +125°C; over a total ionizing dose of 100krad(Si) with exposure at a high dose rate of 50 to 300rad(Si)/s; or over a total ionizing dose of 50krad(Si) with exposure at a low dose rate of <10mrad(Si)/s. (Continued)

| PARAMETER                 | TEST CONDITIONS                                                                  | MIN<br>( <u>Note 13</u> ) | ТҮР | MAX<br>( <u>Note 13</u> ) | UNIT |

|---------------------------|----------------------------------------------------------------------------------|---------------------------|-----|---------------------------|------|

| BUFFER AMPLIFIER          |                                                                                  |                           | L   |                           |      |

| Gain-Bandwidth Product    | $C_L = 1\mu F, I_{SOURCE} = 1mA, A_V = 1, V_{OUT} = 1.25V$<br>( <u>Note 12</u> ) |                           | 200 |                           | kHz  |

| Source Current Capability |                                                                                  |                           |     | 20                        | mA   |

| Sink Current Capability   |                                                                                  | 250                       | 400 |                           | μΑ   |

| Offset Voltage            |                                                                                  | -4                        | 0   | 4                         | mV   |

| IMON CURRENT MONITOR      | I                                                                                | -1                        | I   | łł.                       |      |

| IMON Sense Time           |                                                                                  | 145                       | 225 | 300                       | ns   |

| IMON Output Current Gain  | I <sub>LOAD</sub> = 1A/power stage, LXx off time >300ns                          |                           | 100 |                           | μΑ/Α |

| IMON Gain Accuracy        | I <sub>LOAD</sub> = 1A/power stage, LXx off time >300ns                          | -14                       |     | 14                        | μΑ   |

NOTES:

10. Typical values shown are not guaranteed.

11. The 0A to 9A output current range may be reduced by minimum LXx on-time and minimum LXx off-time specifications.

12. Limits established by characterization or analysis and are not production tested.

13. Parameters with MIN and/or MAX limits are 100% tested at -55°C, +25°C and +125°C, unless otherwise specified.

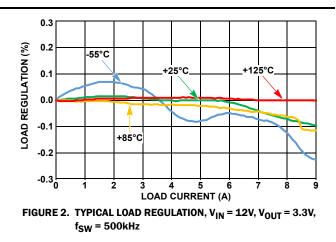

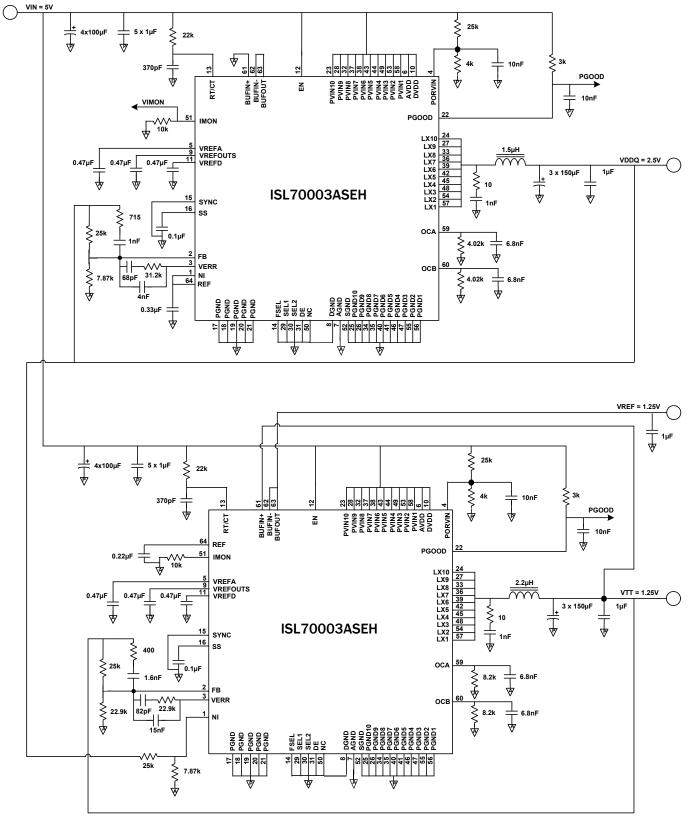

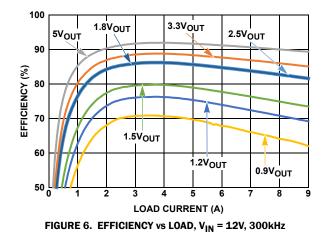

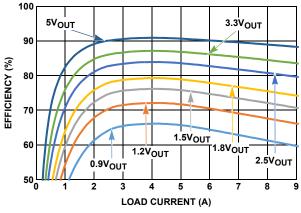

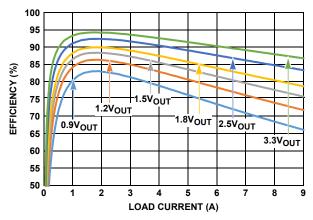

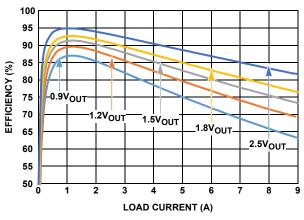

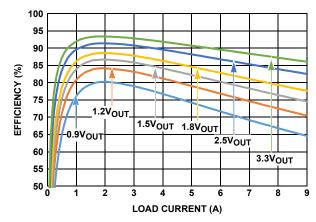

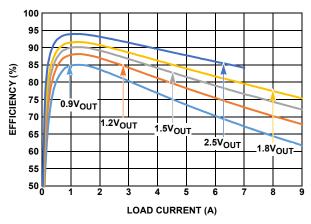

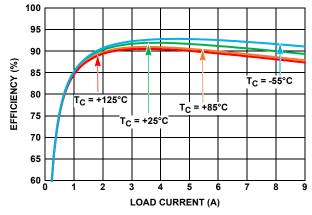

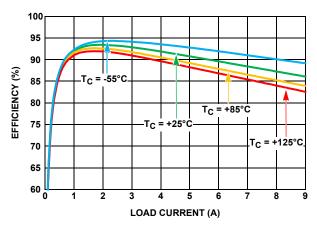

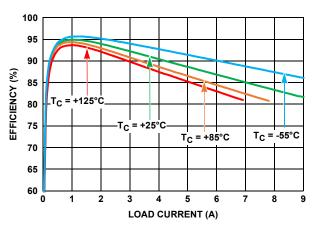

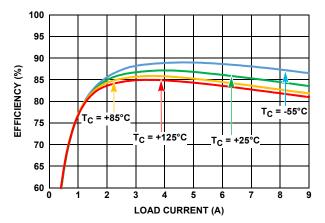

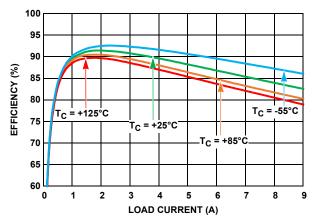

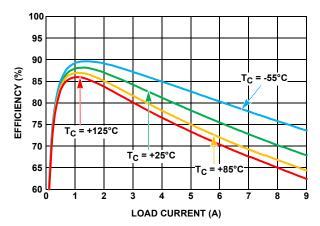

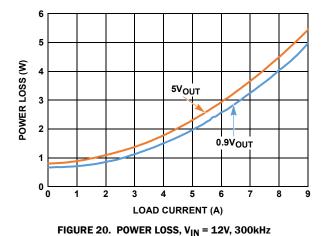

**Typical Performance Curves** Unless otherwise noted, test platform is the ISL70003ASEHEV1Z where  $V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$ ,  $I_{OUT} = 3A$ ,  $f_{SW} = 500$  kHz,  $C_{IN} = 4x \ 100\mu$ F +  $5x1\mu$ F,  $L_{OUT} = 3.3\mu$ H,  $C_{OUT} = 1x \ 150\mu$ F +  $1\mu$ F,  $T_{CASE} = +25$ °C, all outputs active.

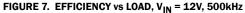

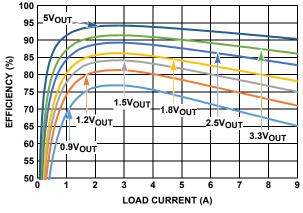

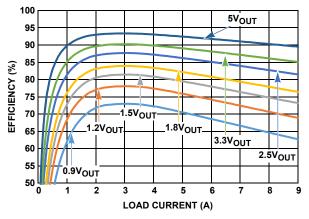

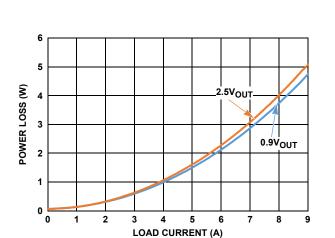

**Typical Performance Curves Unless otherwise noted**, test platform is the ISL70003ASEHEV1Z where  $V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$ ,  $I_{OUT} = 3A$ ,  $f_{SW} = 500$ kHz,  $C_{IN} = 4x \ 100\mu$ F +  $5x1\mu$ F,  $L_{OUT} = 3.3\mu$ H,  $C_{OUT} = 1x \ 150\mu$ F +  $1\mu$ F,  $T_{CASE} = +25^{\circ}$ C, all outputs active. **(Continued)**

FIGURE 8. EFFICIENCY vs LOAD, VIN = 8V, 300kHz

FIGURE 9. EFFICIENCY vs LOAD, VIN = 8V, 500kHz

FIGURE 10. EFFICIENCY vs LOAD, VIN = 5V, 300kHz

FIGURE 12. EFFICIENCY vs LOAD, VIN = 3.3V, 300kHz

FIGURE 11. EFFICIENCY vs LOAD, VIN = 5V, 500kHz

FIGURE 13. EFFICIENCY vs LOAD, VIN = 3.3V, 500kHz

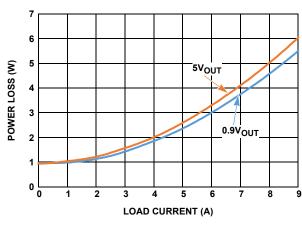

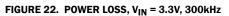

**Typical Performance Curves** Unless otherwise noted, test platform is the ISL70003ASEHEV1Z where  $V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$ ,  $I_{OUT} = 3A$ ,  $f_{SW} = 500$ kHz,  $C_{IN} = 4x \ 100\mu$ F +  $5x1\mu$ F,  $L_{OUT} = 3.3\mu$ H,  $C_{OUT} = 1x \ 150\mu$ F +  $1\mu$ F,  $T_{CASE} = +25$ °C, all outputs active. (Continued)

FIGURE 14. EFFICIENCY vs LOAD,  $V_{IN}$  = 12V,  $V_{OUT}$  = 5V, 300kHz

FIGURE 16. EFFICIENCY vs LOAD, VIN = 5V, VOUT = 3.3V, 500kHz

FIGURE 18. EFFICIENCY vs LOAD, VIN = 3.3V, VOUT = 2.5V, 300kHz

FIGURE 15. EFFICIENCY vs LOAD, VIN = 12V, VOUT = 3.3V, 500kHz

FIGURE 17. EFFICIENCY vs LOAD,  $V_{IN}$  = 5V,  $V_{OUT}$  = 2.5V, 500kHz

FIGURE 19. EFFICIENCY vs LOAD, VIN = 3.3V, VOUT = 1.2V, 500kHz

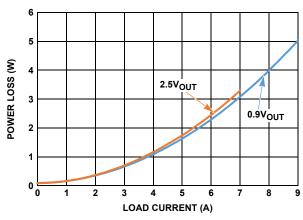

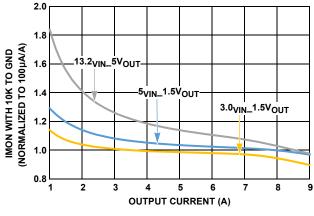

FIGURE 24. LOAD REGULATION vs V<sub>OUT</sub>, PVIN = 12V

FIGURE 21. POWER LOSS,  $V_{IN}$  = 12V, 500kHz

FIGURE 23. POWER LOSS, VIN = 3.3V, 500kHz

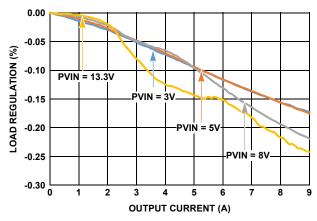

FIGURE 25. LOAD REGULATION vs PVIN, V<sub>OUT</sub> = 1.0V

**Typical Performance Curves** Unless otherwise noted, test platform is the ISL70003ASEHEV1Z where  $V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$ ,  $I_{OUT} = 3A$ ,  $f_{SW} = 500$ kHz,  $C_{IN} = 4x \ 100\mu$ F +  $5x1\mu$ F,  $L_{OUT} = 3.3\mu$ H,  $C_{OUT} = 1x \ 150\mu$ F +  $1\mu$ F,  $T_{CASE} = +25^{\circ}$ C, all outputs active. (Continued)

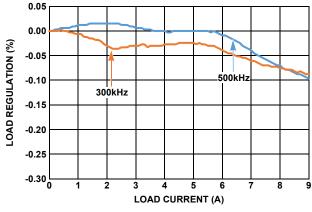

FIGURE 26. LOAD REGULATION vs SWITCHING FREQUENCY

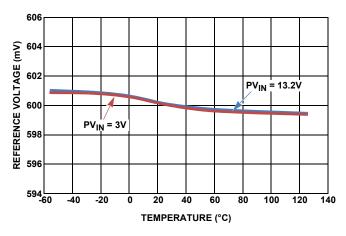

FIGURE 28. REFERENCE VOLTAGE vs TEMPERATURE

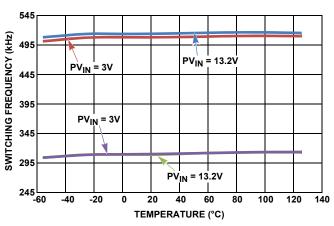

FIGURE 30. SWITCHING FREQUENCY vs TEMPERATURE

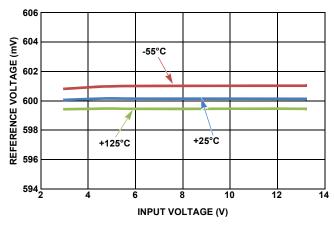

FIGURE 29. REFERENCE VOLTAGE vs VIN

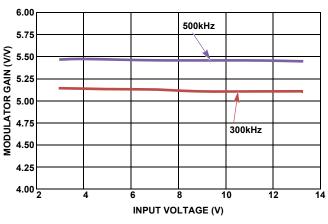

FIGURE 31. MODULATOR GAIN vs VIN

**Typical Performance Curves** Unless otherwise noted, test platform is the ISL70003ASEHEV1Z where  $V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$ ,  $I_{OUT} = 3A$ ,  $f_{SW} = 500$ kHz,  $C_{IN} = 4x \ 100 \mu F + 5x1 \mu F$ ,  $L_{OUT} = 3.3 \mu$ H,  $C_{OUT} = 1x \ 150 \mu F + 1\mu F$ ,  $T_{CASE} = +25^{\circ}C$ , all outputs active. (Continued)

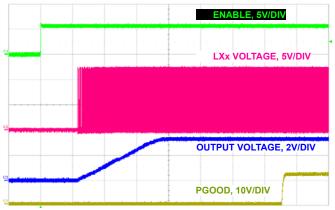

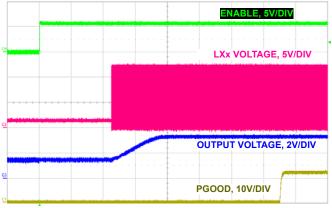

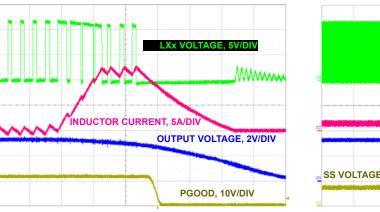

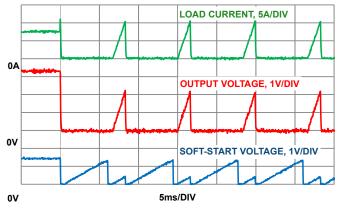

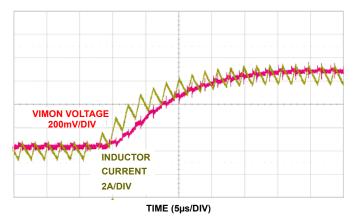

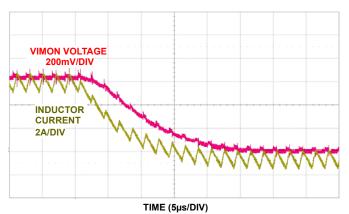

FIGURE 32. MONOTONIC SOFT-START WITH NO LOAD, CCM

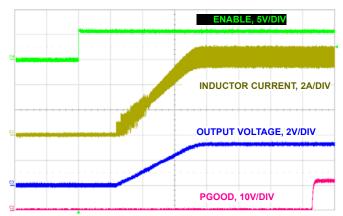

FIGURE 33. MONOTONIC SOFT-START WITH 6A LOAD, CCM

FIGURE 35. MONOTONIC SOFT-START WITH NO LOAD, DEM

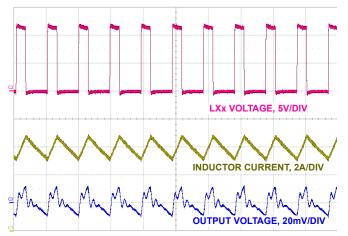

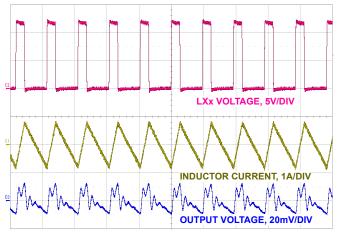

FIGURE 37. STEADY STATE OPERATION 6A LOAD, CCM

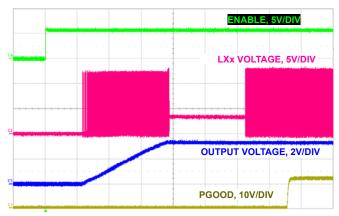

FIGURE 34. MONOTONIC SOFT-START WITH 1.5V PREBIASED LOAD

FIGURE 36. STEADY STATE OPERATION NO LOAD, CCM

**Typical Performance Curves** Unless otherwise noted, test platform is the ISL70003ASEHEV1Z where  $V_{IN}$  = 12V,  $V_{OUT}$  = 3.3V,  $I_{OUT}$  = 3A,  $f_{SW}$  = 500kHz,  $C_{IN}$  = 4x 100 $\mu$ F + 5x1 $\mu$ F,  $L_{OUT}$  = 3.3 $\mu$ H,  $C_{OUT}$  = 1x 150 $\mu$ F + 1 $\mu$ F,  $T_{CASE}$  = +25°C, all outputs active. (Continued)

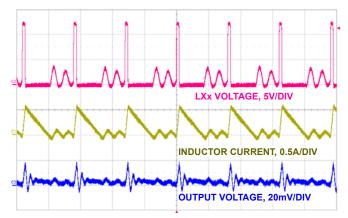

FIGURE 38. DIODE EMULATION OPERATION, V<sub>OUT</sub> = 1.2V, 125mA LOAD

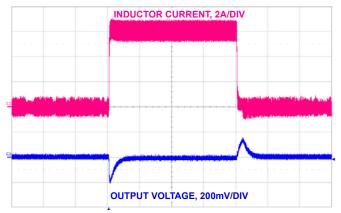

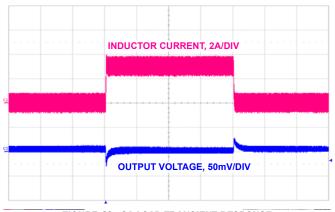

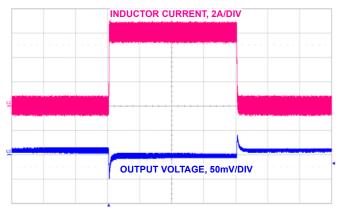

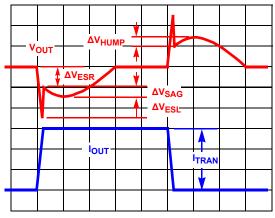

FIGURE 40. 3A LOAD TRANSIENT RESPONSE

FIGURE 41. 6A LOAD TRANSIENT RESPONSE

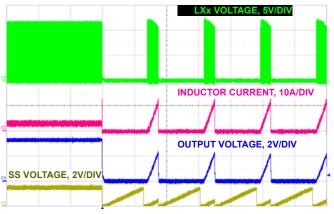

FIGURE 42. OVERCURRENT RESPONSE

FIGURE 43. HICCUP RESPONSE IN OCP

### **Functional Description**

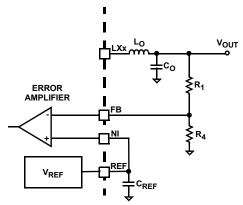

The ISL70003ASEH is a monolithic synchronous buck regulator IC with integrated power MOSFETs. The device utilizes voltage-mode control with feed-forward and switches, at a nominal frequency of 500kHz or 300kHz. It is fabricated on a 0.6µm BiCMOS junction isolated process optimized for power management applications. With this device and a handful of external components, a complete synchronous buck DC/DC converter can be readily implemented. The converter accepts an input voltage ranging from 3V to 13.2V and provides a tightly regulated output voltage ranging from 0.6V to ~90% of the input voltage, at output currents ranging from 0A to 9A. Typical applications include Point-Of-Load (POL) regulation for FPGAs, CPLDs, DSPs, DDR memory, and microprocessors.

#### **Power Blocks**

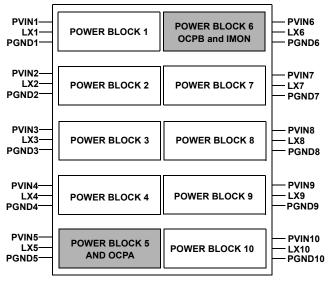

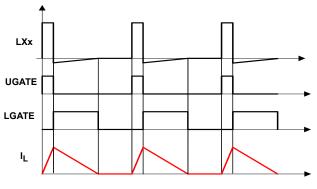

The power output stage of the regulator consists of ten power blocks that are paralleled to provide full 9A output current capability at  $T_J = +125$  °C. The block diagram in Figure 44 shows a top level view of the individual power blocks.

SEL1 and SEL2 pins allow users to disable power blocks in order to reduce switching losses in light-load applications. Depending on the state of these pins the ISL70003ASEH can operate with 2, 4, or 10 active power blocks and also be placed in a sleep mode.

Each power block has a power supply input pin, PVINx, a phase output pin, LXx, and a power supply ground pin, PGNDx. All PVINx pins must be connected to a common power supply rail and all PGNDx pins must be connected to a common ground. LXx pins should be connected to the output inductor based on the required load current and the state of the SEL1, SEL2 pins, but must include the LX5 and LX6 pins. The unused LXx pins should be left unconnected.

Scaled pilot devices associated with Power Blocks 5 and 6 provide current feedback for overcurrent detection and the IMON current monitor feature. Power Blocks 5 and 6 must be connected to the output inductor at all times for proper operation.

### Initialization

The ISL70003ASEH initializes based on the state of the EN input and POR input. Successful initialization prompts a soft-start interval and the regulator begins slowly ramping the output voltage. Once the commanded output voltage is within the proper window of operation, the power-good signal changes state from low to high indicating proper regulator operation.

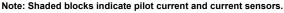

#### Enable

The EN pin accepts TTL/CMOS logic input as described in the Electrical Specifications table on page 10. When the voltage on the EN pin exceeds its logic rising threshold, the controller monitors the POR voltage before initiating the soft-start function for the PWM regulator. When EN is pulled low, the device enters shutdown mode and the supply current drops to a typical value of 1.5mA. All internal power devices are held in a high impedance state while in Shutdown mode. Due to the internal 5V clamp, the EN pin should be driven no higher than 5V or excessive leakage current may be seen on the pin. In standalone applications, the EN pin may be tied to an input voltage >5V through a 50k $\Omega$  resistor to minimize the current into the EN pin. The current should not be allowed to exceed 160µA at any operating voltage.

FIGURE 45. ENABLE TO VIN FOR >5.0V INPUT VOLTAGE

#### **Power-On Reset**

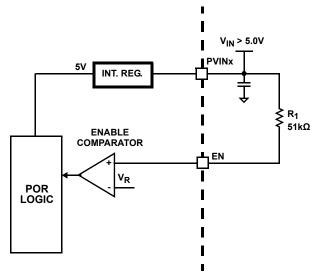

After the EN input requirements are met, the ISL70003ASEH remains in shutdown until the voltage at the POR pin rises above its threshold. The POR circuitry prevents the controller from attempting to soft-start before sufficient bias is present at the PVINx pins.

As shown in Figure 46 on page 21, the POR circuit features a comparator type input. The POR circuit allows the level of the input voltage to precisely gate the turn-on/turn-off of the regulator. An internal I<sub>POR</sub> current sink with a typical value of 12µA is only active when the voltage on the POR pin is below the enable threshold so it can pull the POR pin low. As V<sub>IN</sub> rises, the POR enable level is set by the resistor divider (R<sub>1</sub> and R<sub>2</sub>) from V<sub>IN</sub> and the internal sink current source, I<sub>POR</sub>.

FIGURE 46. POR CIRCUIT

Equation 2 defines the relationship between the resistor divider, sink current, and POR rising level (V<sub>PORR</sub>).

$$V_{PORR} = V_{R} \cdot \left[ 1 + \frac{R_{1}}{R_{2}} \right] + I_{POR} \cdot R_{1}$$

(EQ. 2)

Once the voltage at the POR pin reaches the enable threshold, the  $I_{POR}$  current sink turns off.

With the part enabled and the  $I_{POR}$  current sink off, the falling level ( $V_{PORF}$ ) is set by the resistor divider network and is defined by Equation 3.

$$V_{PORF} = V_{R} \cdot \left[ 1 + \frac{R_{1}}{R_{2}} \right]$$

(EQ. 3)

The difference between the POR rising and falling levels provides adjustable hysteresis so that noise on  $V_{\mbox{\rm IN}}$  does not interfere with the enabling or disabling of the regulator.

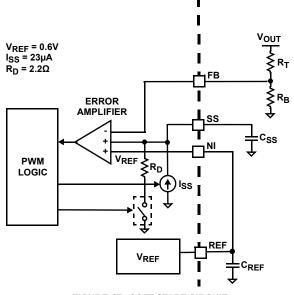

#### Soft-Start

The ISL70003ASEH soft-start function uses an internal current source and an external capacitor to reduce stresses and surge current during start-up.

Once the POR and enable circuits are satisfied, the regulator waits 32 clock cycles and then initiates a soft-start. Figure 47 shows that the soft-start circuit clamps the error amplifier reference voltage to the voltage on an external soft-start capacitor connected to the SS pin. The soft-start capacitor is charged by an internal  $I_{SS}$  current source. As the soft-start capacitor is charged, the output voltage slowly ramps to the set point determined by the reference voltage and the feedback network. Once the voltage on the SS pin is equal to the internal reference voltage, the soft-start interval is complete. Following the soft-start output ramp interval is defined in Equation 4 and is adjustable from approximately 2ms to 200ms. The value of the soft-start capacitor, C<sub>SS</sub>, should range from 82nF to 8.2µF, inclusive. The peak inrush current can be computed from

Equation 5. The soft-start interval should be selected long enough to insure that the peak inrush current plus the peak output load current does not exceed the overcurrent trip level of the regulator.

$$t_{SS} = C_{SS} \cdot \frac{V_{REF}}{I_{SS}}$$

(EQ. 4)

$$I_{\text{INRUSH}} = C_{\text{OUT}} \cdot \frac{V_{\text{OUT}}}{t_{\text{SS}}}$$

(EQ. 5)

The soft-start capacitor is immediately discharged by a  $3.0\Omega$  resistor whenever POR conditions are not met or EN is pulled low. The soft-start discharge time is equal to 256 clock cycles.

FIGURE 47. SOFT-START CIRCUIT

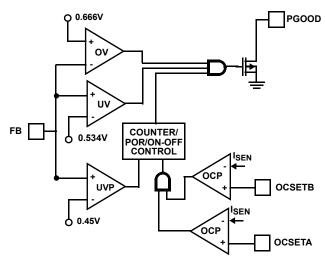

#### **Power-Good**

A power-good indicator is the final step of initialization. After a successful soft-start, the PGOOD pin releases and the voltage rises with an external pull-up resistor. The power-good signal transitions low immediately when the EN pin is pulled low.

The PGOOD pin is an open-drain, logic output and can be pulled up to any voltage from OV to 13.2V. The pull-up resistor should have a nominal value from  $1k\Omega$  to  $10k\Omega$ . The PGOOD pin should be bypassed to DGND with a 10nF ceramic capacitor to mitigate SEE.

### **Fault Monitoring and Protection**

The ISL70003ASEH actively monitors the output voltage and current to detect fault conditions. Fault conditions trigger protective measures to prevent damage to the regulator and the external load device. One common power-good indication signal is provided for linking to external system monitors. The schematic in Figure 48 on page 22 outlines the interaction between the fault monitors and the power-good signal.

#### **Undervoltage and Overvoltage Monitor**

The power-good pin (PGOOD) is an open-drain logic output which indicates that the converter is operating properly and the output voltage is within a set window. The Undervoltage (UV) and Overvoltage (OV) comparators create the output voltage window. The power-good circuitry monitors the FB pin and compares it to the rising and falling thresholds shown in the "Electrical Specifications" table on page 12. If the feedback voltage exceeds the typical rising limit of 111% of the reference voltage, the PGOOD pin pulls low. The PGOOD pin continues to pull low until the feedback voltage falls to a typical of 107.5% of the reference voltage. If the feedback voltage drops below a typical of 89% of the reference voltage, the PGOOD pin pulls low. The PGOOD pin continues to pull low until the feedback voltage rises to a typical 92.5% of the reference voltage. The PGOOD pin then releases and signals the return of the output voltage within the power-good window.

FIGURE 48. POWER-GOOD AND OC PROTECTION CIRCUITRY

#### **Undervoltage Protection**

A hysteretic comparator monitors the FB pin of the regulator. The feedback voltage is compared to an undervoltage threshold that is a fixed percentage of the reference voltage, typically 75%. Once the comparator trips, indicating a valid undervoltage condition, an undervoltage counter increments. The counter is reset if the feedback voltage rises back above the undervoltage threshold plus a specified amount of hysteresis outlined in the "Electrical Specifications" table on page 12. If there are four consecutive undervoltage protection logic shuts down the regulator, pulling PGOOD low.

After the regulator shuts down, it enters a delay interval, approximately equivalent to 512 clock cycles plus one soft-start interval, allowing the device to cool. The undervoltage counter is reset entering the delay interval. The protection logic initiates a normal soft-start once the delay interval ends. If the output successfully soft starts, the power-good signal goes high and normal operation continues. If undervoltage conditions continue to exist during the soft-start interval, the undervoltage counter must overflow before the regulator shuts down again. This Hiccup mode continues indefinitely until the output soft starts successfully.

#### **Overcurrent Protection**

A pilot device integrated into the PMOS transistor of Power Blocks 5 and 6 sample the current each cycle. This current feedback is scaled and compared to an overcurrent threshold based on the resistor value tied from pins OCSETA and OCSETB to AGND.

Upon detection of an overcurrent condition, the upper MOSFET will be immediately turned off and will not be turned on again until the next switching cycle. Upon detection of the initial overcurrent condition, the overcurrent fault counter is set to "1". If, on the subsequent cycle, another overcurrent condition is detected, the OC fault counter will increment. However, if the sampled current falls below the threshold the counter is reset. If there are four sequential OC fault detections, the counter will overflow and the regulator will be shut down under an overcurrent fault condition, pulling PGOOD low.

FIGURE 49. OVERCURRENT BEHAVIOR IN HICCUP MODE

After the regulator shuts down, it enters a delay interval, allowing the device to cool. The delay interval is approximately equal to 512 clock cycles plus one soft-start interval. The overcurrent counter is reset entering the delay interval. The protection logic initiates a normal soft-start once the delay interval ends. If the output successfully soft starts, the power-good signal goes high and normal operation continues. If overcurrent conditions continue to exist during the soft-start interval, the overcurrent counter must overflow before the regulator shutdowns the output again. This Hiccup mode continues indefinitely until the output soft starts successfully (see Figure 49).

#### **Load Regulation**

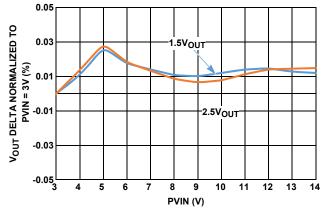

The ISL70003ASEH is a metal only revision of the ISL70003SEH specifically to improve load regulation across the wider 9A output current rating. Although the load regulation is now improved by an order of magnitude, there are performance generalities to be aware of; higher temperature, lower PVIN, and higher VOUT/PVIN ratio all yield tighter load regulation performance. The switching frequency has no deterministic effect, producing differences one order of magnitude less than the other condition considerations. Figure 2 on page 1 and Figures 24, 25, 26, 27 on page 17 illustrate performance trends for a sampling of these conditions.

### **Application Information**

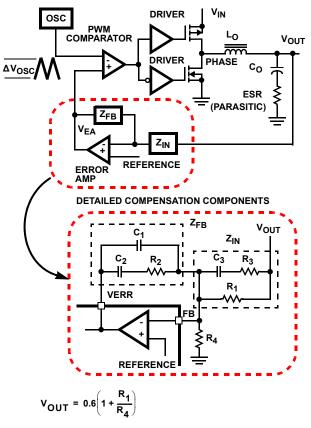

#### **Voltage Feed-Forward**

Feed-forward is used to maintain a constant modulator gain and achieve optimum loop response over a wide input voltage range. A resistor from PVINx to RT/CT and a capacitor from RT/CT to PGNDx are used to adjust the amplitude of the sawtooth ramp proportional to the input voltage. The capacitor value must be chosen so that it is large enough for mitigation of single-event transients, but low enough for the internal MOSFET device to pull the pin to ground. The following table gives the recommended values for R<sub>T</sub> and C<sub>T</sub> for a given switching frequency. These values will achieve a constant modulator gain across the complete input voltage range.

| FSEL STATE | f <sub>SW</sub> (kHz) | R <sub>T</sub> (kΩ) | C <sub>T</sub> (pF) | MODULATOR<br>GAIN (TYP) |

|------------|-----------------------|---------------------|---------------------|-------------------------|

| 0          | 500                   | 22                  | 370                 | 5                       |

| 1          | 300                   | 36                  | 370                 | 4.8                     |

#### **Switching Frequency Selection**

There are a number of variables to consider when choosing the switching frequency. A high switching frequency increases the switching losses, but may lead to a decrease in output filter size. A lower switching frequency may increase efficiency, but may lead to more output voltage ripple and increased output filter size.

On the ISL70003ASEH, the internal switching frequency is determined by the state of the FSEL pin. This pin is to be tied either high to DVDD for 300kHz or low to GND for 500kHz switching frequency.

#### **Synchronization**

The ISL70003ASEH, can be synchronized to an external clock with a frequency range of 500kHz  $\pm$ 15% or 300kHz  $\pm$ 15%, depending on the state of the FSEL pin.